双冗余CAN总线模块设计主要包括硬件与软件设计两部分。为实现冗余功能,硬件上需要有几个相同可独立工作的设备支持;软件上要具备错误检测和动态切换功能,且切换时间要尽可能短。

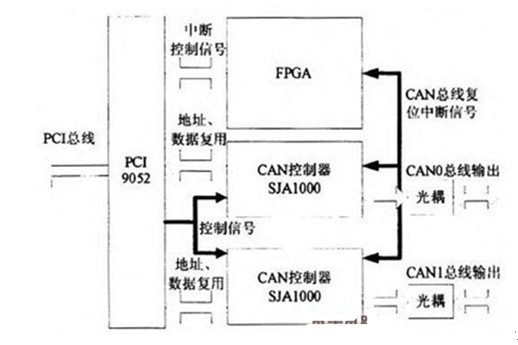

以下为一款双冗余CAN总线模块设计原理电路图。

在本设计中,双冗余CAN总线模块硬件配置两个独立的CAN控制器,并有FPGA对其进行控制,软件通过读取CAN总 线状态寄存器判断是否进行冗余切换动作。下面将详细描述双冗余CAN总线模块的硬件与软件设计,以及冗余功能的实现细节。

我们选择PCI9052作为接口芯片,利用功能芯片实现硬件的逻辑和物理实现。CAN控 制器采用PHILIPS的SJAl000,可工作于BasicCAN模式或PeI.CAN模式下,其中PeIiCAN模式支持CAN 2.0B协议,采用8位地址/数据复用总线接口。

PC J总线双CAN接口卡由两片SJAl000提供两路独立的CAN接口,每片芯片的8位地址/数据总线和读写控制信号。锁存信号直接与PCI9052相连。 SJAl000输出信号经过光耦到CAN收发器PCA82C250,82C250供电电源为隔离电源,由隔离电源转换模块提供。CAN总线的复位信号由FPGA提供,CAN控制器SJAl000的中断信号输出到FPGA.

总线模块设计原理电路图