未来的SerDes设计,嗯,有点恐怖

老wu最近在搜寻高速连接线缆的资料,想找一找关于传输10Gbps数字信号的高速线缆供应商和PCB设计注意事项。

期间在有油管看到这份视频《SerDes And Its Role in Future Designs HD》讲的很是不错,老wu认真做了笔记,这里将该视频从油管搬运回来分享给大家。

未来的SerDes设计会是怎样子的?嗯,有点恐怖,随着云端应用越来越普及,其使用量也水涨船高,促使众多网络供应商必须年年升级其数据中心内部网络的带宽。目前主流的100G互联正逐渐被新一代400G技术所取代,而800G互联技术更已经近在眼前。带宽需求连年暴涨,其底层的高速SerDes技术也因此备受瞩目。

目前,速度最快的SerDes单一通道的带宽已达112Gbps,支持PAM4编码。如此高的速率,使得在整个系统中实现高速信号布线会面临许多许多设计难题。过去通常只是在组件级进行设计考量,而新一代多Gbps设计需要对信号通道路径进行整体分析。研发人员不能只关注一个组件,而是必须分析并优化所有组件在整个通道中的相互作用。

通道中的每个组件都包含一些设计变量,其会影响通道中其他组件的性能。必须考虑插入损耗、回波损耗、串扰、阻抗等连接器变量。PCB设计决策包括布局、布线、材料/层压材料选择、迹线长度与阻抗匹配,它们都能够提高或降低高速串行通道的性能。

设计和优化高速通道需要两个基本步骤。工程师必须为通道中的每个具体组件建立模型。合并这些组件模型即可创建通道模型,从而建立完整的系统。然后在28Gbps以上的数据速率条件下对系统模型进行仿真、建模、分析与测试。

这份《SerDes And Its Role in Future Designs HD》对PCB SerDes设计需要考量的几个问题点进行了比较全面的讲解:

- PCB 板材

- 叠层

- 串扰

- 玻纤效应

- 残桩和背钻技术

- 铜箔粗糙度

- 插损、回损、远端串扰、近端串扰

- 旁路去耦电容寄生电感问题

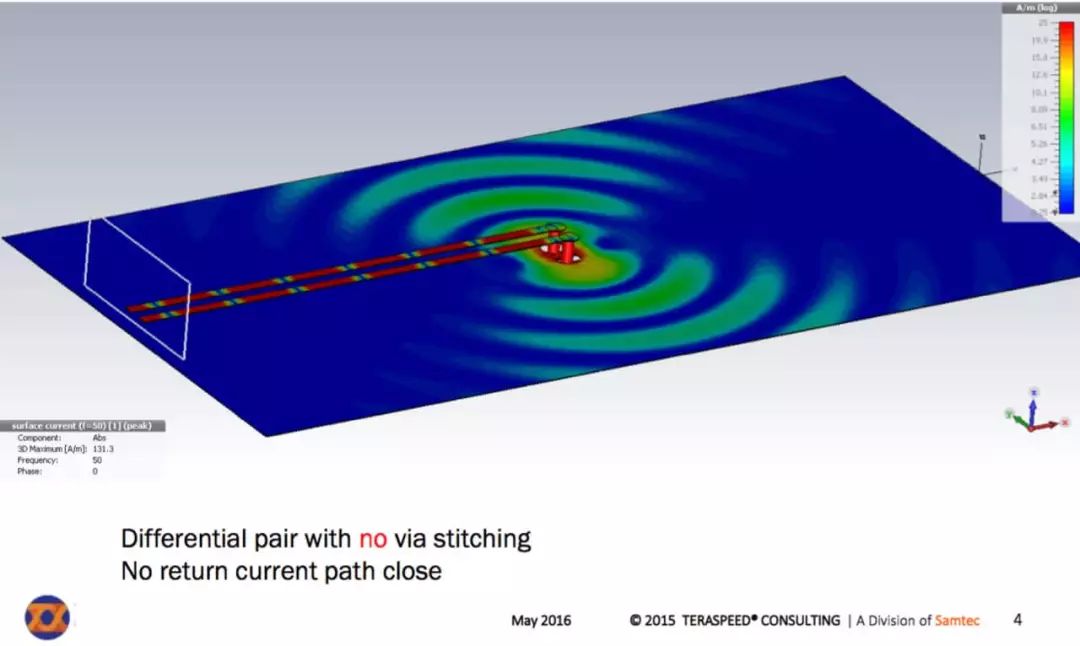

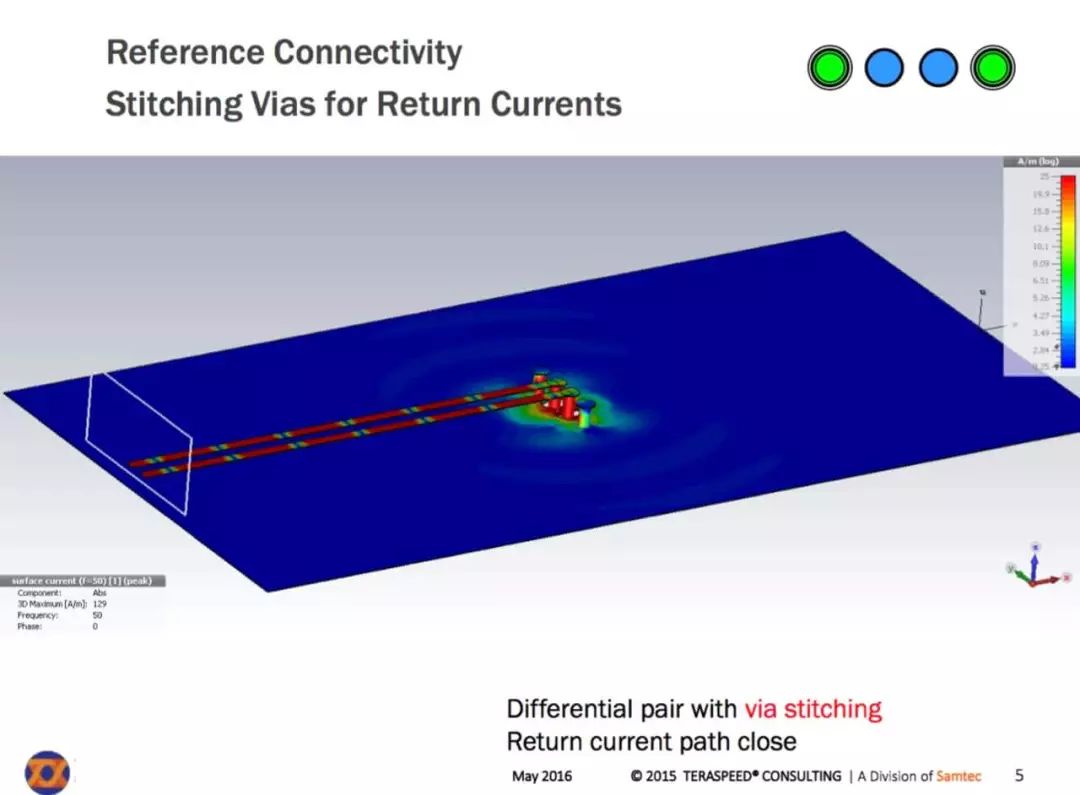

视频中有关于差分线信号回流的3D仿真讲解老wu觉得很不错,之前看差分对的介绍文章,有说到应用差分线的优势,就是差分线对之间可以彼此实现对方信号的回流而不需要参考平面,但视频中通过3D仿真讲解了差分线回流的情况。

虽然差分电路对于类似地弹以及其它可能存在于电源和地平面上的噪音信号是不敏感的。地平面的部分回流抵消并不代表差分电路就不以参考平面作为信号返回路径,其实在信号回流分析上,差分走线和普通的单端走线的机理是一致的,即高频信号总是沿着电感最小的回路进行回流,最大的区别在于差分线除了有对地的耦合之外,还存在相互之间的耦合,哪一种耦合强,那一种就成为主要的回流通路。

在PCB 电路设计中,一般差分走线之间的耦合较小,往往只占10~20%的耦合度,更多的还是对地的耦合,所以差分走线的主要回流路径还是存在于地平面。当地平面发生不连续的时候,无参考平面的区域,差分走线之间的耦合才会提供主要的回流通路。尽管参考平面的不连续对差分走线的影响没有对普通的单端走线来的严重,但还是会降低差分信号的质量,增加EMI,要尽量避免。

高于高速差分线stitching via的设计

在实现高速设计时,高速信号的输路径中的物理几何结构的任何微小的不连续都会显着降低信号质量。 这种降级包括信号幅度的损失,信号上升时间的减少和抖动的增加。 因此,必须识别高速通道中的这些不连续,并提供减轻其影响的方法,以实现更好的信号传输。其中,元器件封装焊盘,连接器和信号打孔换层都会会造成阻抗不连续及回流路径的变化,这时需要为信号的过孔提供额外的接地过孔为其提供连续的回流路径。

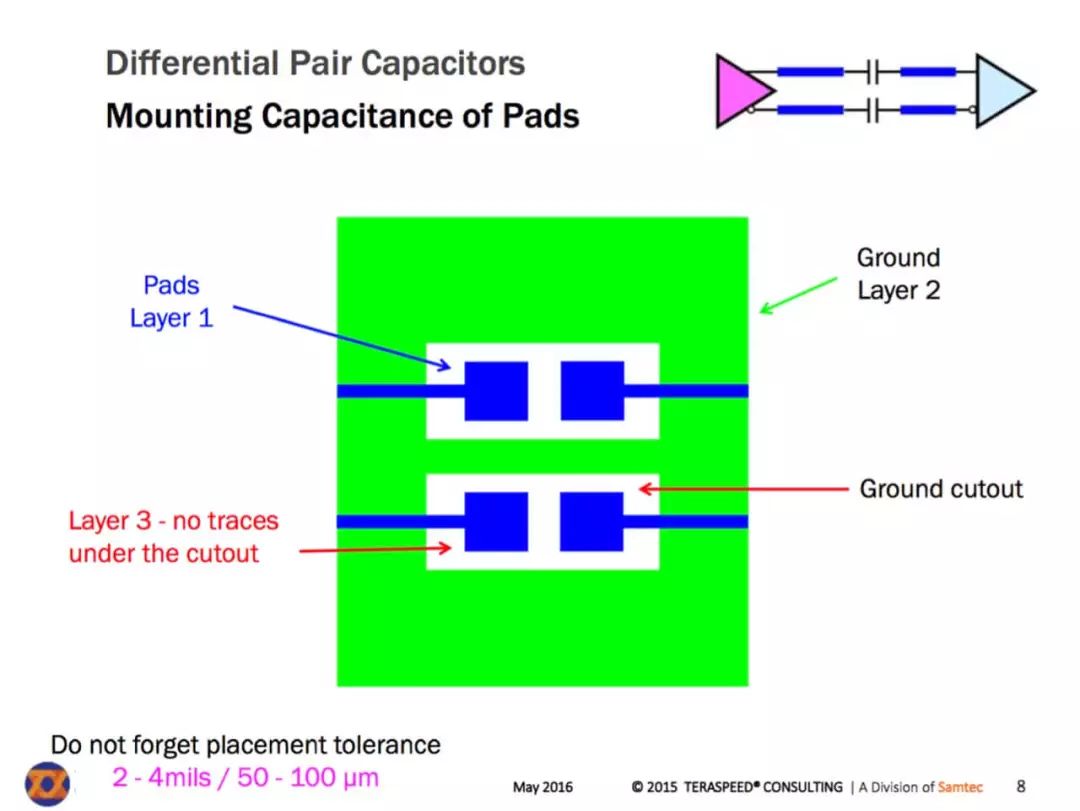

焊盘参考平面挖空

同样是为了阻抗的连续性,为了减少焊盘与参考平面的寄生电容,隔直电容是高速串行通道中阻抗不连续的常见来源。关于优化焊盘阻抗不连续问题,可以参考 Altera的Application Note 530《Optimizing Impedance Discontinuity Caused by Surface Mount Pads for High-Speed Channel Designs》,老wu已经上传的网盘,大家可以参考文章末尾给出的下载方法下载,那参考平面的铜皮该挖空多少合适?视频中也有人提出这个问题,回答是依仿真结果,依不同的层叠结构而不同,最好进行3D仿真。

背钻技术

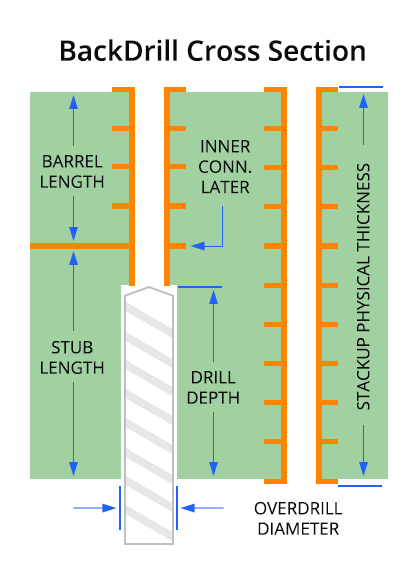

可控深度钻孔(CDD),也称为背钻孔。它可以将未使用的铜质筒体或分叉短线从印刷电路板通孔中去除。当高速信号在PCB板层之间传输时穿过了一个铜质筒体,就会产生失真。如果信号层中存在分叉短线,并且该短线较长,失真将会成为严重的问题。

在制造完成后,可使用稍大的钻头重钻这些孔,去除分叉短线。将孔背钻至可控的深度,接近但不触及过孔使用的最后一层。考虑到制造和材料差异,好的制作商可使背钻孔的遗留短线达到7mil,理想的剩余短线长度应小于10mi。

PCB玻纤效应

PCB基材是由树脂、玻纤、铜箔、填料等压合而成,玻纤布的编号是按照纬纱宽度、经纱的宽度,纬纱之间的间隙,以及经纱之间的间隙,进行编号定义的。玻纤布,对信号的影响,主要来自于介电常数不一样。

通过视频中的PPT,我们可以看到一对儿差分线,其中一根儿走在玻璃纤维上,一根儿走在纤维空隙中。因为介质的介电常数不一样,造成两根传输线的阻抗不一样,这导致俩风险: 一是阻抗不匹配,二是信号传输速度不一样,对于25Gbps以上的信号会导致严重的信号失真。

铜箔粗糙度

信号高速/高频化是信号传输越来越集中于导线“表层”(称为趋肤效应),当频率达1GHz时,其信号在导线表面的传输厚度仅为2.1μm,如果导体表面粗糙度为3-5μm,信号传输仅在粗糙度的厚度范围内进行;当信号传输频率提高到10GHz时,其信号在导体表面的传输厚度为0.7μm,信号传输更是在粗糙度范围内进行。信号在粗糙度范围传输,传输信号的驻波、反射将越来越严重,并导致信号传输路径变长,损耗增加。当然,改善铜箔粗糙度对高速信号的影响,需要板厂来帮助我们解决该问题。

当然,高速SerDes应用的PCB设计要点还有很多,老wu这里就不一一列举了,视频讲得很好,建议大家多看看,还有一些额外的知识点和视频对应的PPT文档老wu放网盘里了,有兴趣的同学可以关注公众号:吴川斌的博客,在公众号里回复:下载|高速SerDes应用PCB设计要点,即可获得下载链接。

最后,感慨下,老是听闻软件开发的同学感慨,求求软件开发技术栈别再更新了,老了,真学不动了,其实,硬件何尝不是这样呢?

© 本文经作者吴川斌授权,原文(点此跳转)

利用捷多邦 - 解决PCB打样所有问题

用梦想Layout,为Idea制板,以行动焊接

从灵感到实物,捷多邦助您快人一步

在线PCB打样请认准:www.jdbpcb.com

微信下单请扫描二维码,更快更省更轻松