(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。

(2)打印时总是不能打印到一页纸上:

a. 创建pcb库时没有在原点;

b. 多次移动和旋转了元件,pcb板界外有隐藏的字符。选择显示所有隐藏的字符, 缩小pcb, 然后移动字符到边界内。

(3)DRC报告网络被分成几个部分:表示这个网络没有连通,看报告文件,使用选择CONNECTED COPPER查找。另外提醒朋友尽量使用WIN2000, 减少蓝屏的机会;多几次导出文件,做成新的DDB文件,减少文件尺寸和PROTEL僵死的机会。如果作较复杂得设计,尽量不要使用自动布线。

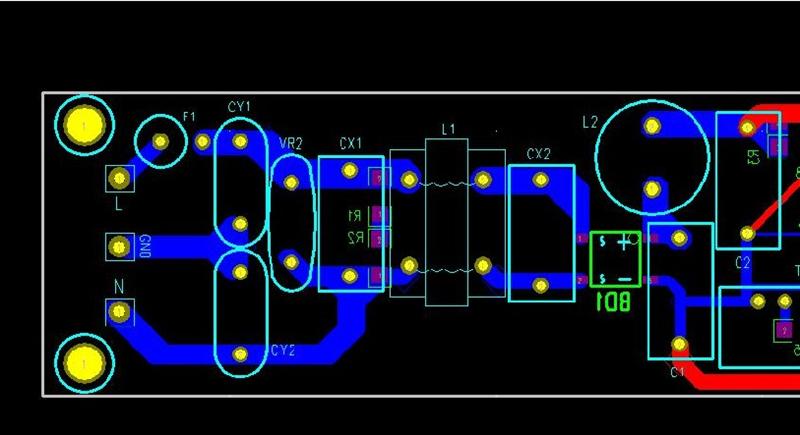

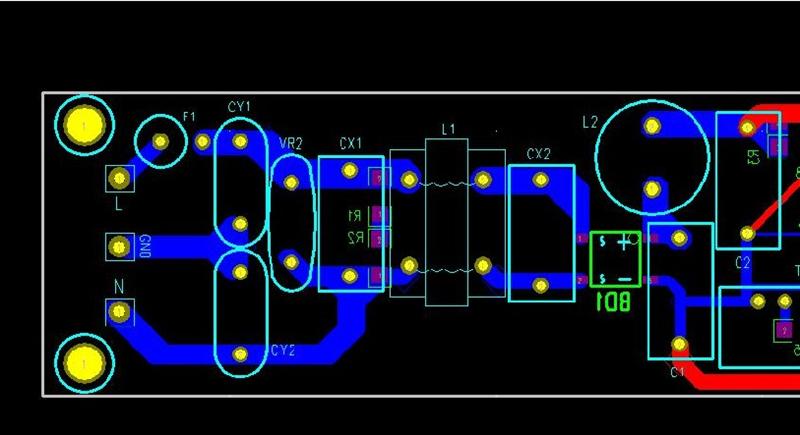

在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的, 在整个PCB中,以布线的设计过程限定最高,技巧最细、工作量最大。PCB布线有单面布线、 双面布线及多层布线。布线的方式也有两种:自动布线及交互式布线,在自动布线之前, 可以用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应避免相邻平行, 以免产生反射干扰。必要时应加地线隔离,两相邻层的布线要互相垂直,平行容易产生寄生耦合。

自动布线的布通率,依赖于良好的布局,布线规则可以预先设定, 包括走线的弯曲次数、导通孔的数目、步进的数目等。一般先进行探索式布经线,快速地把短线连通, 然后进行迷宫式布线,先把要布的连线进行全局的布线路径优化,它可以根据需要断开已布的线。 并试着重新再布线,以改进总体效果。

对目前高密度的PCB设计已感觉到贯通孔不太适应了, 它浪费了许多宝贵的布线通道,为解决这一矛盾,出现了盲孔和埋孔技术,它不仅完成了导通孔的作用, 还省出许多布线通道使布线过程完成得更加方便,更加流畅,更为完善,PCB 板的设计过程是一个复杂而又简单的过程,要想很好地掌握它,还需广大电子工程设计人员去自已体会, 才能得到其中的真谛。