SDRAM电路简介

SDRAM电路有很多的设计要领,在这里只讲解一些基础的知识,我们应该注意,SDRAM电路应该按照公共端时钟同步系统时序去很好的设计,串联22/33欧完全是电阻是为了和源端阻抗相匹配,靠近源端放置能够有效匹配传输线阻抗,这样就很好打的使得信号输出功率最大,信噪比高。这样电阻还可以衰减回波,减小振铃。但是这也造成了电阻(配合分布电容)使得信号边沿变缓,降低速率的缺点。

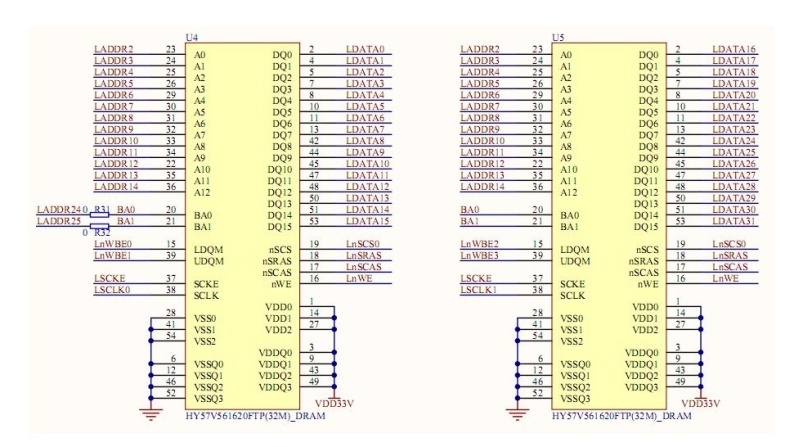

SDRAM电路设计技巧

因为地址线和控制线都是单向的,所以很容易确定源端和远端,只要在源端放置电阻即可。不可是,数据线是双向的,无法确定哪头儿是源,哪头儿是目的,如何放置呢?干脆就不放,一来,把电阻放远端根本起不到匹配作用,二来,布线也会徒增烦恼。有一种说法是“谁的上升沿的时间更少,就该靠近谁”,此法有益消除回波,减缓边沿(使谐波变少),不失为补救之策,不知然否?

陡峭边沿的谐波多,此类信号比较“脏”,容易污染板内电磁环境,是故需积极避免之。正弦波乃最纯净之信号,可以经常使用。

注意:时钟线和重要信号线必须单独使用匹配电阻,地址线可以使用排阻减小板面积。

SDRAM电路设计的要点在于正确取得/设置有效数据(时钟沿落在有效数据位上,参考电压稳定,电平判决正确)。 SDRAM可以调线,减少交叉走线。这样才能做到更好一些。

更多的PCB设计技巧,可以到捷多邦官网(www.jdbpcb.com)进行了解和参考